随着边缘AI应用蓬勃发展,从智能手机、物联网设备到自动驾驶,市场对高性能、低功耗、小体积芯片的需求日益严苛。全球芯片代工大厂联电在Semicon Taiwan的演讲活动上剖析了边缘AI所面临的双重带宽挑战,并揭示其正积极转型,以先进的3D垂直堆栈与封装解决方案,突破传统2D平面设计的物理极限,引领半导体产业迈向新纪元。

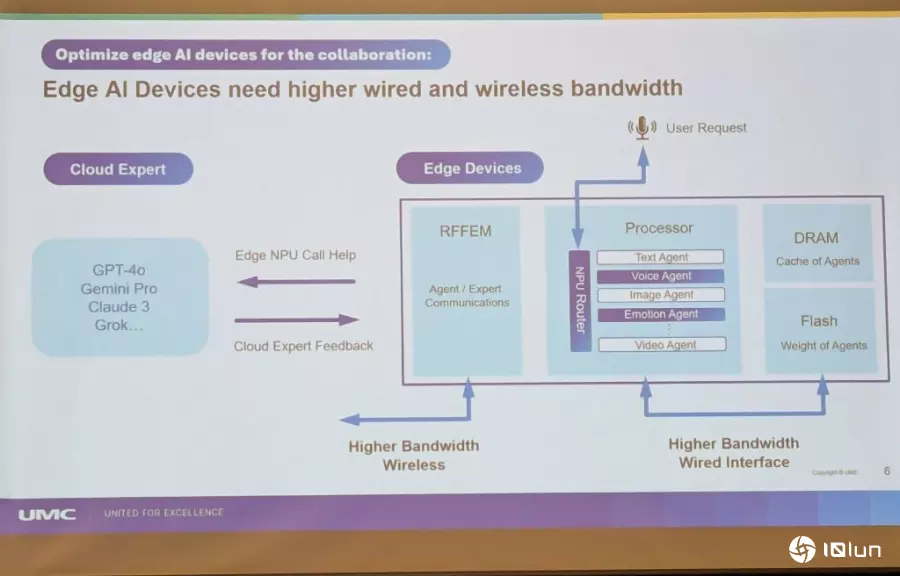

联电先进封装业务部技术开发总监王裕平指出,Edge AI设备正陷入一个有趣的两难困境。一方面,当设备需要调用云计算服务器的强大算力进行协同运算(Call for help)时,需要极高的对外无线通信带宽。另一方面,设备内部的AI代理人(Agent)在进行复杂的即时运算与决策时,处理器与内存之间也需要极高的对内数据传输带宽。

应对这种内外夹击的带宽需求,这对传统的2D平面芯片设计构成了巨大挑战。若要提升对外通信能力,就必须增加射频前端模块(RF Front-end Module),但这会导致芯片面积急剧扩大。同样地,为了增强内部运算性能,AI代理人需要搭配大量的DRAM作为缓存(Cache)、Flash存储权重(Weights),这些组件在传统PCB电路板上各自占据空间,不仅使得整体功耗与体积难以缩减,更限制了性能的进一步提升。传统设计思维已然触及物理与成本的双重天花板。

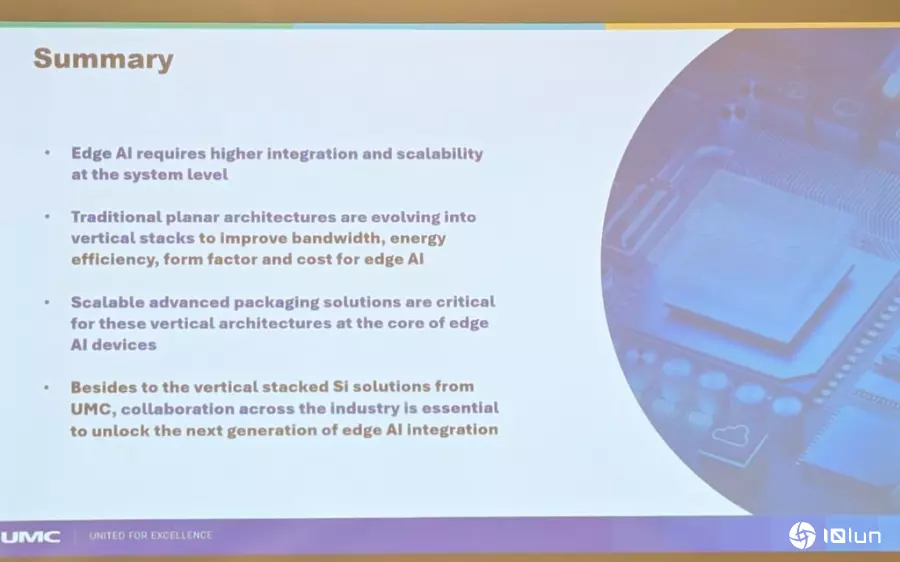

王裕平表示,为解决此困境,联电提出了根本性的解决方案,那就是从2D走向3D。他比喻道,在宇宙中两点之间最短的距离,或许不是一条直线,而是将空间折叠起来。这个概念完美诠释了3D垂直堆栈技术的核心优势。而通过将不同的功能芯片(如处理器、内存、射频模块)垂直堆栈并互联,能够实现极致的尺寸缩减,这相较于将所有组件在同一平面上展开,垂直堆栈能大幅缩小芯片的整体体积,满足边缘设备对轻薄短小的严苛要求。

另外,还有更短的传输路径,使得信号在垂直方向上的传输距离远短于在平面上的绕线距离,这直接带来了更低的延迟与更高的传输速度。还有,优异的能源效率,这依赖传输路径缩短,信号损耗与驱动所需功耗显著降低,从而大幅提升了整体的能源效率,延长了边缘设备的电池续航力。

对此,王裕平解释了联电的模块化构建边缘AI芯片,其中将复杂的系统解构成四个关键的“积木”(Building Blocks),电源管理芯片(PMIC)、射频前端模块、处理器及内存,并通过3D堆栈技术将它们高效集成。而实现上述愿景的背后,是联电深厚的特殊制程技术积累。尤其,联电正将其独特的特殊技术,转化为可规模化的先进封装解决方案。

王裕平强调,在“硅中介层(Silicon Interposer)”技术上,联电不仅能提供纯硅中介层,更进一步集成了深沟槽电容,为高带宽运算提供了绝佳的信号与电源完整性(Signal and Power Integrity)。其次,针对异质集成的需求,联电的“硅穿孔后期(TSV-last)”技术、芯片薄化(Wafer Thinning)与混合键合(Hybrid Bonding)技术,使其能够接收来自客户或第三方(如DRAM制造商)的芯片,在联电的厂房内进行精密的垂直集成。目前,联电已成功将外部的DRAM内存芯片与自家的逻辑芯片结合,打造出极具成本效益的AI推论引擎(Inference Engine),充分验证了其技术能力。

王裕平强调最后指出,Edge AI的系统级集成极其复杂,需要整个生态系的通力合作。联电深知,仅凭一己之力无法完成这场技术变革。因此,联电正积极与EDA模拟软件供应商、设备制造商以及后段封装测试(OSAT)伙伴展开深度合作,共同打造一个完整、高效的解决方案平台。

(首图来源:官网)配资论坛登录入口官网

泓阈资本提示:文章来自网络,不代表本站观点。